Universidade de Aveiro

# Manual de Utilizador Placa DETIUA-S3

Versão 1.0

Manuel Almeida

manuel.almeida@ieeta.pt

## Conteúdos

| 1. Ir | ntrodução                     | 3                     |

|-------|-------------------------------|-----------------------|

| 1.1.  | Informação acerca do manual   | 3                     |

| 1.2.  | Referências                   | 5                     |

| 2. A  | rquitectura da Placa          | 6                     |

| 2.1.  | Alimentação                   | 6                     |

| 2.2.  | FPGA                          | 7                     |

| 2.3.  | CPLD                          | 8                     |

| 2.4.  | Módulo USB                    | 8                     |

| 2.5.  | Memória <i>Flash</i>          | 10                    |

| 2.6.  | Oscilador                     | 11                    |

| 2.7.  | JTAG                          | 11                    |

| 2.8.  | Barramentos de Expansão       | 13                    |

| 3. F  | uncionamento da PlacaError! E | Bookmark not defined. |

## 1. Introdução

## 1.1. Informação acerca do manual

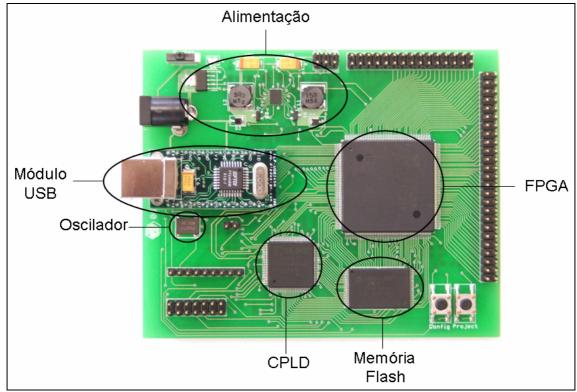

Este manual tem por objectivo descrever os componentes constituintes da placa de prototipagem e respectivas interfaces. É possivel ver como os dispositivos estão interligados na placa e como a FPGA os acede e controla.

Os componentes e interfaces discutidos aqui são:

- Alimentação

- FPGA Spartan-3

- Módulo USB

- CPLD

- Memória Flash

- Botão de pressão

- Relógio

- JTAG

- Barramento de Expansão

O manual permite, ao utilizador da placa, perceber o funcionamento da mesma e fornecer os dados necessários ao utilizador para uma correcta utilização.

Componentes da placa

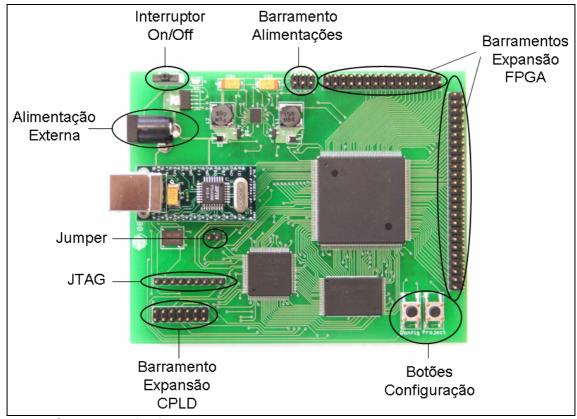

Conectores da placa

## 1.2. Referências

As seguintes referências citam documentos ou endereços electrónicos que contêm informações mais detalhadas dos componentes utilizados na placa de prototipagem.

FPGA Spartan-3 Datasheet

http://www.xilinx.com/bvdocs/publications/ds099.pdf

Arquitectura e Configuração

http://direct.xilinx.com/bvdocs/appnotes/xapp452.pdf

**CPLD Datasheet**

http://www.xilinx.com/bvdocs/publications/ds057.pdf

Alimentação

http://www.ti.com/

Módulo USB: Datasheet e Drivers

http://www.dlpdesign.com/

Memória Flash

http://www.amd.com/

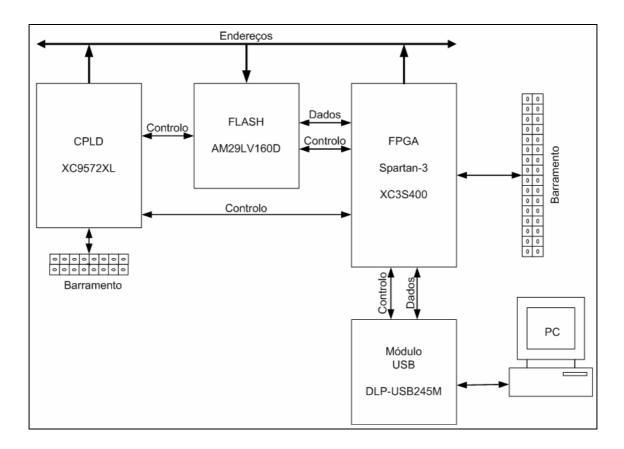

## 2. Arquitectura da Placa

## 2.1. Alimentação

A alimentação da placa é realizada através da porta USB de um computador ou de um transformador de 6V DC utilizando um conector de 2.1mm, onde o contacto interior é o negativo.

A placa utiliza reguladores de tensão para obter as tensões necessárias ao bom funcionamento. As tensões necessárias são 5V, 3.3V, 2.5V e 1.2V.

Quando a placa se encontra ligada à porta USB, esta fornece a alimentação. A partir do momento que se liga a alimentação exterior, o *jack* desliga a alimentação feita pela porta USB e passa a fornecer a alimentação a partir de um transformador.

A placa tem um interruptor que permite ligar e desligar, onde é possivel verificar o estado da mesma através de um *led*. Se a placa se encontrar ligada o *led* vermelho acende.

## 2.2. FPGA

A FPGA Spartan-3 da Xilinx (XC3S400-4-PQ208) utilizada como componente reconfigurável, contém 400 mil portas de sistema, 56Kb de RAM distribuída, 16 multiplicadores, 141 pinos de entrada e saída, etc.

Ela está directamente ligada:

- Controlador USB

- Memória Flash

- CPLD

- Barramento de Expansão

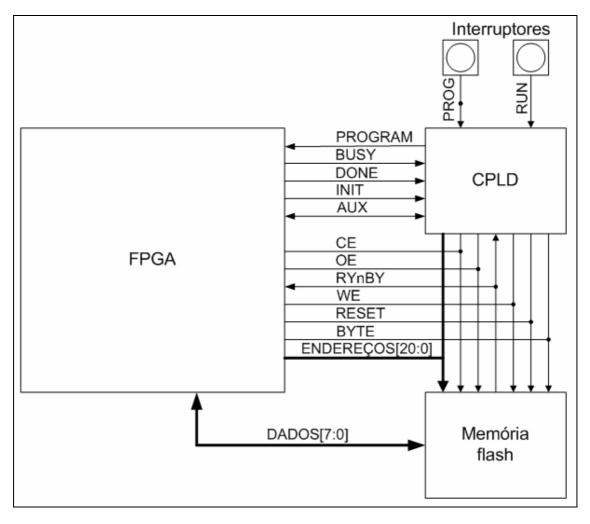

## 2.3. CPLD

A placa contém uma CPLD XC9572XL da Xilinx, que é utilizada no processo de configuração da FPGA.

A memória *flash* contém o ficheiro de configuração (*bitstream*) da FPGA, sendo necessário um componente, neste caso uma CPLD, que realize o controlo da memória *flash* de modo a permitir a configuração da FPGA.

| Descrição       | Pinos CPLD                                                                                                         | Pinos FPGA                                                                                                              |

|-----------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| ENDEREÇOS[20:0] | p35, p29, p28, p13,<br>p50, p49, p42, p41,<br>p40, p39, p37, p36,<br>p25, p20, p18, p17,<br>p16, p15, p14, p9, p12 | p52, p64, p65, p95,<br>p42, p43, p44, p45,<br>p46, p48, p50, p51,<br>p71, p76, p77, p78,<br>p85, p93, p94, p102,<br>p97 |

| CE              | p26                                                                                                                | p65                                                                                                                     |

| OE              | p28                                                                                                                | p64                                                                                                                     |

| RYnBY           | p15                                                                                                                | p40                                                                                                                     |

| WE              | p11                                                                                                                | p37                                                                                                                     |

| RESET           | p12                                                                                                                | p39                                                                                                                     |

| ВҮТЕ            | p47                                                                                                                | p62                                                                                                                     |

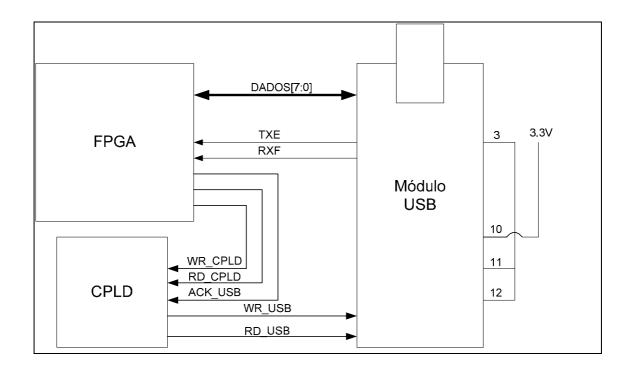

## 2.4. Módulo USB

Manuel Almeida 8 01-08-2006

O módulo USB utilizado foi o DLP-USB245M, que é um interface USB-FIFO paralelo. Este módulo da empresa DLP Design, tem como componente central o FT245BM da FTDI.

O módulo foi configurado por forma a funcionar a uma tensão de 3.3V, apesar de ser alimentado a 5V. Os dados são controlados através dos pinos TXE, RXF, WR e RD.

Este módulo USB contém uma EEPROM que possibilita armazenar a descrição do produto ou o número de série. Esta potencialidade, foi aproveitada para a introdução dessas informações, possibilitando que, ao ser ligadas várias placas a um computador, este consiga determinar quantas e quais as placas que estão num dado momento ligadas.

| Descrição  | Pinos da FPGA               |

|------------|-----------------------------|

| DADOS[7:0] | p4,p5,p7, 9,p10,p11,p12,p13 |

| TXE        | р3                          |

| RXF        | p2                          |

| WR         | p39                         |

| RD         | p40                         |

- TXE Com o nível lógico '1' significa que o buffer de transmissão\* está cheio ou então está ocupado a escrever o último byte. Neste caso, estar a '1', não se deve escrever para o buffer de transmissão. Só com o nível lógico a '0' é que se pode escrever para o buffer de transmissão.

- RXF Com o nível lógico '0', o buffer de recepção\*\* contém pelo menos um byte e está pronto a ler através do RD. O RXF passa ao nível '1' quando o buffer de recepção está vazio.

- WR Na transição de '1' para '0' o módulo lê os 8 bits de dados e escreve o byte no buffer de transmissão.

- RD Quando colocado no nível lógico '0' o módulo lê do buffer de recepção um byte. Colocado no nível lógico '1' os pinos de dados ficam no estado de alta impedância.

- \* Buffer de transmissão é um buffer intermédio que recebe dados vindo da FPGA e que serão posteriormente enviados para a porta USB.

- \*\* Buffer de recepção é um buffer intermédio que recebe dados vindos da porta USB e que será posteriormente lidos pela FPGA.

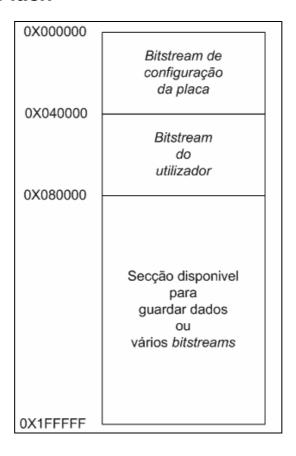

## 2.5. Memória Flash

A placa utiliza uma memória *flash* de 16 Mbit com a referência AM29LV160. Esta memória é constituída por 31 sectores de 64Kbytes, 1 de 32Kbytes, 1 de 16Kbytes e 2 de 8Kbytes.

| Descrição  | Pinos FPGA                             |

|------------|----------------------------------------|

| DADOS[7:0] | p67, p68, p72, p74, p86, p87, p90, p92 |

Se por algum motivo a primeiro sector da memória *flash* for alterado a placa não funcionará correctamente, ou ficará inutilizada.

## 2.6. Oscilador

A placa utiliza um oscilador de 80 MHz. Este sinal de relógio é utilizado pela FPGA e pela CPLD, num dos pinos de *global clock*.

| Descrição | Pino da FPGA |

|-----------|--------------|

| CLOCK     | p79          |

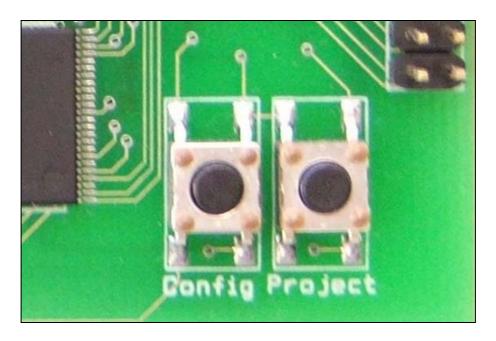

## 2.7. Botões de Pressão

Existe dois botões de pressão na placa, onde um tem o nome de *Config* e o outro *Project*. O botão *Config* permite ao utilizador configurar a placa com o ficheiro de configuração por defeito. O botão *Project* permite ao utilizador configurar a placa com um ficheiro de configuração pretendido.

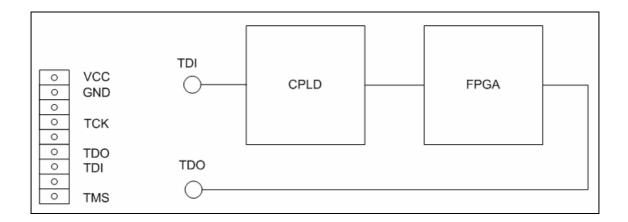

#### 2.8. JTAG

A placa está dotada de um conector que disponibiliza pinos dedicados, que são usados para configurar a FPGA e a CPLD. Este modo de configuração Boundary Scan, mais conhecido como JTAG, permite uma configuração directa sendo apenas necessário o cabo multilinx e a ferramenta IMPACT da Xilinx.

Ao utilizar o JTAG, vai aparecer uma corrente de configuração onde aparece primeiro a CPLD e posteriormente a FPGA. Nesta forma, o primeiro dispositivo a ser possível configurar é a CPLD. Para configurar a FPGA não é necessário ter que configurar a CPLD, devido existir uma opção na ferramenta IMPACT que possibilita saltar para o próximo dispositivo.

## 2.9. Barramentos de Expansão

| Pinos conector 1 | Pinos FPGA | Pinos conector 1 | Pinos FPGA |

|------------------|------------|------------------|------------|

| 1                | p106       | 26               | p139       |

| 2                | p107       | 27               | p140       |

| 3                | p108       | 28               | p141       |

| 4                | p109       | 29               | p143       |

| 5                | p111       | 30               | p144       |

| 6                | p113       | 31               | p146       |

| 7                | p114       | 32               | p147       |

| 8                | p115       | 33               | p148       |

| 9                | p 116      | 34               | p149       |

| 10               | p117       | 35               | p150       |

| 11               | p119       | 36               | p152       |

| 12               | p120       | 37               | p154       |

| 13               | p122       | 38               | p155       |

| 14               | p123       | 39               | p156       |

| 15               | p124       | 40               | p161       |

| 16               | p125       | 41               | p162       |

| 17               | p126       | 42               | p165       |

| 18               | p128       | 43               | p166       |

| 19               | p130       | 44               | p167       |

| 20               | p131       | 45               | p168       |

| 21               | p132       | 46               | p169       |

| 22               | p133       | 47               | p171       |

| 23               | p135       | 48               | p172       |

| 24               | p137       | 49               | p175       |

| 25               | p138       | 50               | p176       |

| Pinos conector 2 | Pinos FPGA | Pinos conector 2 | Pinos FPGA |

|------------------|------------|------------------|------------|

| 1                | p178       | 16               | p199       |

| 2                | p180       | 17               | p200       |

| 3                | p181       | 18               | p203       |

| 4                | p182       | 19               | p204       |

| 5                | p183       | 20               | p205       |

| 6                | p184       | 21               | p15        |

| 7                | p185       | 22               | p16        |

| 8                | p187       | 23               | p18        |

| 9                | p189       | 24               | p19        |

| 10               | p190       | 25               | p20        |

| 11               | p191       | 26               | p21        |

| 12               | p194       | 27               | p22        |

| 13               | p196       | 28               | p24        |

| 14               | p197       | 29               | p26        |

| 15               | p198       | 30               | p27        |

| Pinos conector<br>CPLD | Pinos CPLD | Pinos conector<br>CPLD | Pinos CPLD |

|------------------------|------------|------------------------|------------|

| 1                      | p56        | 8                      | p23        |

| 2                      | p58        | 9                      | p27        |

| 3                      | p59        | 10                     | р3         |

| 4                      | p60        | 11                     | p4         |

| 5                      | p61        | 12                     | p99        |

| 6                      | p63        | 13                     | 2.5V       |

| 7                      | p64        | 14                     | GND        |

#### 2006

## Universidade de Aveiro

#### **DETI**

Departamento de Electrónica, Telecomunicações e Informática

#### **IEETA**

Instituto de Engenharia Electrónica e Telemática de Aveiro

Laboratório de Sistemas Computacionais

Campus Universitário de Santiago 3810-193 Aveiro Portugal